Простой генератор сигналов

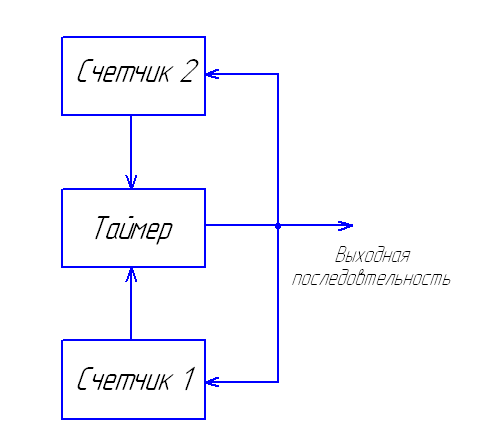

Описание функциональной схемы

Таймер формирует временные интервалы заданной длительности, Счетчик 1 считает эти импульсы, и при необходимости меняет временные интервалы, генерируемые таймером. Счетчик 2 отсчитывает нужное количество импульсов и, досчитав да заданного значения, останавливает таймер.

Алгоритм работы устройства

Таймер Т1 формирует временные интервалы заданной длительности, по окончанию интервала он формирует прерывание, в котором его значения обновляется. Таким образом, можно сформировать любую последовательность импульсов с любыми параметрами (период, длительность, скважность).

Подпрограмма прерывания начинается с проверки – не последний ли это импульс, если последний,таймер останавливается. Если не последний, производится проверка, это имульс или пауза между импульсми (длительность импульса - 2500 мкс, длительность паузы - 7500 мкс), таким образом, поочередно формируются временные интервалы импульса и паузы.

Описание режима CTC

Режим сброса таймера при совпадении (СТС)

В режиме СТС (WGM01, WGM00 = 0b10) регистр OCR0 используется для задания разрешающей способности счетчика. Если задан режим CTC и значение счетчика (TCNT0) совпадает со значением регистра OCR0, то счетчик обнуляется (TCNT0=0). Таким образом, OCR0А задает вершину счета счетчика, а, следовательно, и его разрешающую способность. В данном режиме обеспечивается более широкий диапазон регулировки частоты генерируемых прямоугольных импульсов.

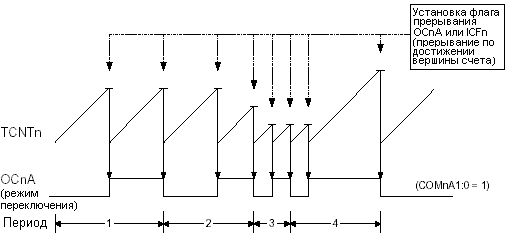

В режиме сброса таймера при совпадении (WGMn3-0 = 0b0100 или 0b1100) пределы счета таймера задаются регистром OCR0A. В режиме СТС происходит сброс счетчика (TCNT0), если его значение совпадает со значением регистра OCR0A. В данном режиме обеспечивается возможность регулировки частоты генерируемых прямоугольных импульсов. Временная диаграмма работы таймера врежиме СТС показана на рисунке 1. Счетчик (TCNTn) инкрементирует свое состояние до тех пор, пока не возникнет совпадение со значением OCR0A , а затем счетчик (TCNT0) сбрасывается.

Рис. 2 Временные диаграммы режима СТС

Помимо сброса при этом может генерироваться прерывание с помощью флагов OCF0A, соответствующим используемым регистрам для задания верхнего предела счета. Если прерывание разрешено, то процедура обработки прерывания может использоваться для обновления верхнего предела счета.

Для генерации сигнала в режиме CTC выход OC0A может использоваться для изменения логического уровня при каждом совпадении, для чего необходимо задать режим переключения (COM0A1, COMA0 = 0b01). Значение OC0A будет присутствовать на выводе порта, только если для данного вывода задано выходное направление. Максимальная частота генерируемого сигнала равна fOC0 = fclk_I/O/2, если OCRnA = 0x0000. Для других значений OCRn частоту генерируемого сигнала можно определить по формуле:

где переменная N задает коэффициент предделителя (1, 8, 32, 64, 128, 256 или 1024).

Программа

.include"m16def.inc"

.org 0

rjmp RESET ; ResetHandler

.org 2

reti; IRQ0 Handler

.org 4

reti;;rjmp EXT_INT1 ;IRQ1 Handler

.org 6

reti;reti;jmp ;TIM2_COMP; Timer2 Compare Handler

.org 8

reti;;reti;jmp ;TIM2_OVF; Timer2 Overflow Handler

.org 10

reti; ;reti;jmp;TIM1_CAPT ; Timer1 Capture Handler

.org 12

jmp TIM1_COMPA ; Timer1CompareA Handler

.org 14

reti;reti;jmp;TIM1_COMPB ; Timer1 CompareB Handler

.org 16

reti;reti;jmp ;TIM1_OVF; Timer1 Overflow Handler

.org 18

reti;;reti;jmp ;TIM0_OVF; Timer0 Overflow Handler

.org 20

reti;;reti;jmp ;SPI_STC; SPI Transfer Complete Handler

.org 22

reti;;reti;jmp;USART_RXC ; USART RX Complete Handler

.org 24

reti;;reti;jmp;USART_UDRE ; UDR Empty Handler

.org 26

reti;reti;jmp ;USART_TXC; USART TX Complete Handler

.org 28

reti;reti;jmp ;ADC ; ADCConversion Complete Handler

.org 30

reti;reti;jmp ;EE_RDY ;EEPROM Ready Handler

.org 32

reti;reti;jmp ;ANA_COMP; Analog Comparator Handler

.org 34

reti;reti;jmp ;TWSI ;Two-wire Serial Interface Handler

.org 36

reti;reti;jmp ;EXT_INT2; IRQ2 Handler

.org 38

reti; Timer0 CompareHandler

.org 40

reti;reti;jmp SPM_RDY ;Store Program Memory Ready Handler

;

RESET:

ldi r16,255

out ddrd,r16

ldi r16,high(2500)

out ocr1ah,r16

ldi r16,low(2500)

out ocr1al,r16

ldir16,(1<<com1a0)

out tccr1a,r16

ldir16,(1<<wgm12)+(1<<cs10)

out tccr1b,r16

ldir16,(1<<ocie1a)

out timsk,r16

ldi r16,high(RAMEND)

out SPH,r16

ldi r16,low(RAMEND)

out SPL,r16 ;èíèöèàëèçàöèÿ ñòåêà

sei ;ðàçðåøåíèå ïðåðûâàíèé

main: ;îñíîâíîé öèêë

rjmp main

TIM1_COMPA:

nop

inc r18

cpi r18,16

breq out_pulse

inc r17

cpi r17,2

breq pulse

ldi r16,high(2500)

out ocr1ah,r16

ldi r16,low(2500)

out ocr1al,r16

out_ret:

reti

pulse:

ldi r17,0

ldi r16,high(7500)

out ocr1ah,r16

ldi r16,low(7500)

out ocr1al,r16

jmp out_ret

out_pulse:

ldi r16,0

out tccr1a,r16

out tccr1b,r16

out portd,r16

jmpout_ret

После запуска микроконтроллера происходит процедура инициализации (RESET), в этой подпрограмме последовательно:

-настраиваются порты ввода-вывода (порт D настраивается на вывод)

-настраивается работа таймера Т1:

-загружаетсячисло (2500) в регистр сравнения

-вывод OC1A настраивается на «переворачивание» уровня при совпадениисчетного регистра и регистра сравнения (OCR1A)

-задается режим работы (сброс по совпадению) и источник тактового сигнала (без предделителя, от системного тактового сигнала)

-разрешается работа прерывания по совпадению Т1

-инициализируется стек (настраивается вершина стека)

-разрешаются прерывания.

На этом инициализация контроллера завершена. Далее счетчик команд «уходит» в основной цикл.

При возникновении прерывания, запускается подпрограмма обработки прерывания TIM1_COMPA, она начинается с увеличения количества прерываний (задана последовательность из восьми импульсов, а это 16 «переворачиваний уровня»), число прерывания сравнивается с 16, и, если равно, запускается подпрограмма out_pulse. В ней останавливается таймер (обнулением управляющих регистров микроконтроллера). Если же число прерываний меньше 16, программа продолжается далее. Производится проверка флага breq pulse, и, если он установлен, запускается подпрограмма pulse, в которой обновляется регистр сравнения (загружается число 7500), и флаг сбрасывается. Таким образом, по наличию флага, поочередно загружаются числа 2500 и 7500, и на выводе OC1A формируется последовательность со скважностью 4 (по заданию).

Принципиальная электрическая схема

Результаты моделирования схемы в программе PROTEUS